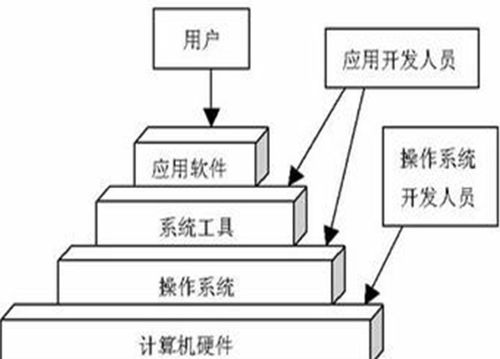

計(jì)算機(jī)系統(tǒng),作為現(xiàn)代信息社會(huì)的核心引擎,其強(qiáng)大的功能建立在精密而復(fù)雜的硬件基礎(chǔ)之上。硬件不僅是計(jì)算機(jī)的物理載體,更是所有軟件指令得以執(zhí)行的最終舞臺(tái)。理解計(jì)算機(jī)系統(tǒng)的硬件組成及其開發(fā)歷程,是洞察信息技術(shù)發(fā)展的關(guān)鍵。

一、計(jì)算機(jī)系統(tǒng)的核心硬件組成

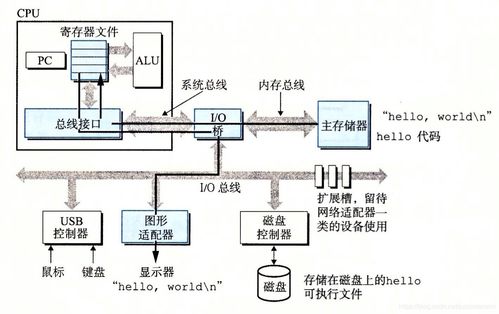

一個(gè)經(jīng)典的計(jì)算機(jī)硬件系統(tǒng),遵循馮·諾依曼體系結(jié)構(gòu),主要由五大功能部件構(gòu)成:

- 運(yùn)算器:作為計(jì)算機(jī)的“算盤”,負(fù)責(zé)執(zhí)行所有的算術(shù)運(yùn)算(如加、減、乘、除)和邏輯運(yùn)算(如與、或、非)。它是中央處理器(CPU)的核心組成部分之一。

- 控制器:相當(dāng)于計(jì)算機(jī)的“指揮中心”。它從內(nèi)存中取出指令,進(jìn)行譯碼和分析,然后向系統(tǒng)的其他部件發(fā)出控制信號(hào),協(xié)調(diào)各部件有序工作。控制器與運(yùn)算器共同構(gòu)成了CPU。

- 存儲(chǔ)器:是計(jì)算機(jī)的“記憶倉庫”,用于存放程序和數(shù)據(jù)。存儲(chǔ)器分為多級(jí):

- 主存儲(chǔ)器(內(nèi)存):直接與CPU交換數(shù)據(jù),速度快但容量有限,斷電后信息丟失。

- 輔助存儲(chǔ)器(外存):如硬盤、固態(tài)硬盤(SSD)、U盤等,用于長(zhǎng)期、大量存儲(chǔ)數(shù)據(jù),速度較慢但容量大,斷電后信息不丟失。

- 高速緩沖存儲(chǔ)器(Cache):位于CPU內(nèi)部或緊鄰CPU,速度極快,用于緩解CPU與內(nèi)存之間的速度矛盾。

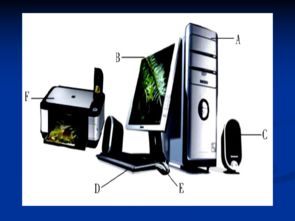

- 輸入設(shè)備:是計(jì)算機(jī)的“感官”,負(fù)責(zé)將外界信息(如文字、圖像、聲音)轉(zhuǎn)換為計(jì)算機(jī)可處理的二進(jìn)制數(shù)據(jù)。常見設(shè)備包括鍵盤、鼠標(biāo)、掃描儀、麥克風(fēng)、攝像頭等。

- 輸出設(shè)備:是計(jì)算機(jī)的“表達(dá)器官”,負(fù)責(zé)將處理后的二進(jìn)制結(jié)果轉(zhuǎn)換為人可感知的形式。典型設(shè)備有顯示器、打印機(jī)、音響等。

連接所有這些部件的系統(tǒng)總線(包括數(shù)據(jù)總線、地址總線和控制總線)構(gòu)成了信息傳輸?shù)摹案咚俟贰保_保了數(shù)據(jù)和控制信號(hào)在各部件間高效流通。

二、計(jì)算機(jī)硬件開發(fā)的演進(jìn)與挑戰(zhàn)

硬件開發(fā)是一個(gè)將抽象設(shè)計(jì)轉(zhuǎn)化為物理實(shí)體的復(fù)雜工程過程,其核心目標(biāo)是追求更高的性能、更低的功耗、更小的體積和更低的成本。其發(fā)展歷程與挑戰(zhàn)主要體現(xiàn)在以下幾個(gè)方面:

1. 集成度的飛躍:從晶體管到芯片

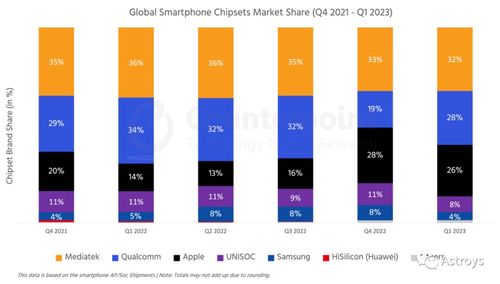

硬件開發(fā)史是一部微型化史。從最初的電子管、晶體管,到小規(guī)模、大規(guī)模集成電路,再到今天的超大規(guī)模集成電路和系統(tǒng)級(jí)芯片(SoC),集成度遵循著“摩爾定律”不斷提升。現(xiàn)代CPU一個(gè)芯片上可集成數(shù)百億個(gè)晶體管,將整個(gè)計(jì)算機(jī)系統(tǒng)的核心功能濃縮于方寸之間。

2. 架構(gòu)創(chuàng)新:提升并行與效率

單純提高主頻已遇到物理瓶頸,硬件架構(gòu)的創(chuàng)新成為關(guān)鍵。

- 多核與眾核:在單個(gè)芯片內(nèi)集成多個(gè)處理核心,實(shí)現(xiàn)真正的并行計(jì)算。

- 專用處理器:如圖形處理器(GPU)、神經(jīng)網(wǎng)絡(luò)處理器(NPU)、張量處理單元(TPU)等,針對(duì)特定計(jì)算任務(wù)(如圖形渲染、AI推理)進(jìn)行硬件級(jí)優(yōu)化,性能遠(yuǎn)超通用CPU。

- 異構(gòu)計(jì)算:將CPU、GPU、NPU等不同架構(gòu)的處理器協(xié)同工作,各司其職,實(shí)現(xiàn)整體效率最大化。

3. 存儲(chǔ)技術(shù)的革新

存儲(chǔ)系統(tǒng)的性能直接制約整機(jī)效率。從機(jī)械硬盤(HDD)到基于閃存的固態(tài)硬盤(SSD),速度實(shí)現(xiàn)了量級(jí)提升。新型非易失性內(nèi)存(如Intel Optane)試圖彌合內(nèi)存與外存之間的鴻溝。內(nèi)存技術(shù)也從DDR系列向更高帶寬、更低功耗的方向持續(xù)演進(jìn)。

4. 開發(fā)流程與工具的現(xiàn)代化

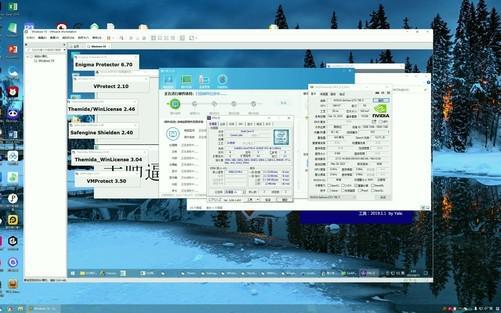

現(xiàn)代硬件開發(fā)高度依賴電子設(shè)計(jì)自動(dòng)化(EDA)工具鏈,涵蓋從系統(tǒng)架構(gòu)設(shè)計(jì)、寄存器傳輸級(jí)(RTL)編碼、邏輯綜合、物理布局布線到仿真驗(yàn)證的全流程。硬件描述語言(如Verilog, VHDL)是工程師的“畫筆”。基于高級(jí)語言(如C/C++)的高層次綜合(HLS)技術(shù),正試圖降低硬件設(shè)計(jì)的門檻。

- 前沿挑戰(zhàn)與未來方向

- 物理極限:晶體管尺寸逼近原子級(jí)別,量子隧穿效應(yīng)等物理限制使得摩爾定律逐漸失效,需要尋找新材料(如碳納米管、二維材料)和新原理(如量子計(jì)算)。

- 功耗墻:性能提升伴隨功耗急劇增加,能效比成為核心指標(biāo),催生了近閾值計(jì)算、三維集成等低功耗技術(shù)。

- 軟硬件協(xié)同設(shè)計(jì):未來的趨勢(shì)不再是硬件先行,而是針對(duì)特定應(yīng)用(如人工智能、自動(dòng)駕駛),從算法和軟件需求出發(fā),定制最優(yōu)的硬件架構(gòu),實(shí)現(xiàn)極致的性能和效率。

****

計(jì)算機(jī)硬件,從宏觀的機(jī)箱、主板到微觀的納米級(jí)晶體管,構(gòu)成了一個(gè)層次分明、協(xié)同工作的精密系統(tǒng)。硬件開發(fā)則是一條永無止境的創(chuàng)新之路,在物理規(guī)律、工程技術(shù)和應(yīng)用需求的共同驅(qū)動(dòng)下不斷突破邊界。它不僅為軟件提供了更強(qiáng)大的舞臺(tái),更在根本上定義了計(jì)算能力的可能性,持續(xù)推動(dòng)著整個(gè)數(shù)字世界向前發(fā)展。